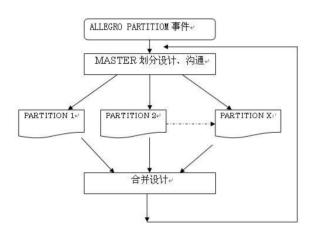

Allegro 产品包中 Allegro Partitioning Option 是一种用于 PCB 团队合作设计的功能模块,它可将一块复杂 PCB 板分成多个简单的 PCB 板,通过团队合作设计,合并设计的方法,可以大大提升设计效率,缩短设计周期。如下图所示:

ALLEGRO PARTITIOM 事件,主要是项目紧急、单板复杂、绿色通道类等单板。

MASTER 需要对单板进行划分、规则定义、预布局以及团队沟通合作。

PATITION 主要对子设计布局布线,子设计任务完成后 MASTER 需要对子设计合并、优化等。当设计不能满要求时,有可能需要再进行并行设计,直到设计符合设计要求。

## 一、创建设计区域 Create Partitions

1. 运行 Place/Design Partition/Create Partition 命令,在Options 窗口显示内容如下图所示:

Partition Data:

Name: Partition 项目名, 不可修改。

Location: 当前目录下的 PCB 文件

Designer:设计者 Administrator

Status:角色

Progress:项目状态

Notes:备注

View Next:浏览下一个设计区域

Apply:划分设计区域完成

Reset:重新设计分区

Partition Commands:

Preview:查看当前设计区域的器件

Refresh:刷新

Workflow Manager:并行设计管理

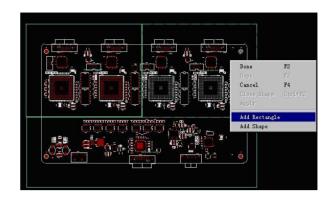

2. 在 PCB 板内合理划分 PCB 设计区域。在 Create Partition 命令运行后,当前命令是直线的方式划分,如需要将设计区域划分成其它复杂区域,需要右击鼠标选择多边形命令,如下图所示:

直线划分

#### 复杂划分

直线划分: 在默认命令时,点击鼠标左键画直线的方式划分设计区域。画直线时软件可自动延伸。

复杂划分: 需右击鼠标选取 Add Rectangle 或 Add Shape 命令,同画多边形铜皮一样来划分设计区域。

3. 查看划分区域。划分好区域后点击 Options 中或右击菜单中的 Apply ,在每个设计区会自动添加 PARTITION\_X 区域名。Options 中的 Next View 激活,点击 Next View 可以选取下一个设计区域,配合 Preview 命令可查看当前区域内的封装信息。如下图所示, Is Shared 为 Yes 时,封装在两个设计区之间。

|              | n Preview Report                                                     | ☐ Match word ☐ Match | C             |

|--------------|----------------------------------------------------------------------|----------------------|---------------|

|              | Name E:/part01/VSP_71<br>ri Jun 22 01:52:06 200<br>Partition Preview |                      | <u>[_4</u>    |

| Refdes       | Component                                                            | Package              | Is<br>Shared? |

|              | Component  CAP NP_SC0603_0.1UF                                       | Package<br>SC0603    | 100           |

| C101         | -                                                                    |                      | 100           |

| C101<br>C102 | CAP NP_SC0603_0.1UF                                                  | SC0603               | 100           |

## 注意事项:

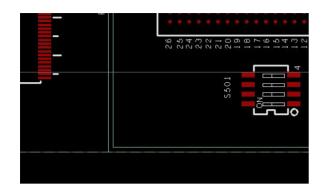

直线划分与复杂划分不能交替用,在复杂划分时,要注意多边形区域之间不要留有间隔,因为小间隔会导致合并设计后,在间隔间的元素会产生 Prop\_Fixd 属性,元素不能编辑,只能通过 SKILL程序删除 Prop\_Fixd 属性,如下图所示。

#### 二、接口规划 GuidePorts

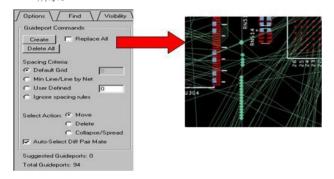

1. 创建 GuidePorts 运行 Place/Design Partition/GuidePorts, Options 中点击 Create。在区域划分线与网络鼠线交点会自动产生 GuidePort,通过 GuidePort 来调整布线通道,如图所示。

Guideport Commands:

Create: 创建 GuidePorts

Replace All:将所有 GuidePorts 刷新

Delete All:删除所有 GuidePorts

Move:移动 GuidePort

Delete:删除 GuidePort

Collapse/spread:伸展方式调整

Spacing Criteria

Default Grid:格点大小调整

Min Line/Line by net:最小线间隔调整

User Defined: 自定义间隔调整

Ignore Spacing rules:不自动调整间隔

2. 调整 GuidePorts。 设置好 Spacing Criteria 方式,点击 Guideport Commands 命令,框选划分线上的 GuidePorts 即可删除、移动及调整。

#### 三、并行设计流程管理

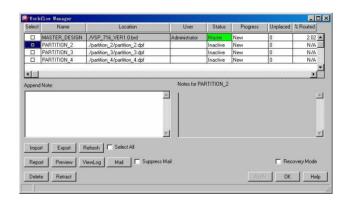

当划分好设计区域和布线通道后,运行 Place/Design Partition/Workflow Manager 进行流程管理。

Workflow Manager:

Select: 中框中打"X"表示选中

Name: 划分区域的名字

Location:保存的目录,可点击修改

User:设计用户。建议用 E-Mail 地址做为 User, 这样每次添加的

Note 都可以发送邮箱

Status:设计区域的状态。Exported:子设计模块已导出;Imported:

子设计模块已导入; Inactive: 初始状态

Progress:进展。New 子设计没有修改; In Progress 子设计设计中: Complete 完成

Unplaced:没有放置的器件数量

%Routed:已完成线比例

Append Note: 备注,选中子设计即可添加备注,以 E-Mail 的方式 发送给 User。不支持中文,第次添加的备注内容都保存

MASTER DESIGN

Import: 导入选中的子设计

Export: 导出选中的子设计

Refresh: 刷新选中子设计内容

Select All:选中所有子设计及 MASTER\_DESIGN

Report:显示选中子设计的进展状态

Preview:显示选中子设计的器件信息

ViewLog:显示处理日志

Mail:发送 E-Mail

Suppress Mail:禁止发送 Mail

Delete:删除选中的子设计

Retract: 撤消选中的子设计

Recovery Mode:恢复模式

Apply: 确定

Help: 帮助

1. 导出子设计

划分好设计区划后, WorkflowManager 窗口中, 会显示出所有的

Partition,即子设计。选中需要导出的子设计,添加好 Note 信息。点击 Export 导出,E-Mail 备注信息给子设计工程师,同时当前目录下会产生多个 Partition\_x 的目录,在每个 Partition目录下有一个\*. dpf 的子设计文件。导出的子设计变灰,不可修改。如下图所示

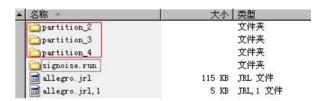

#### 2. 子设计

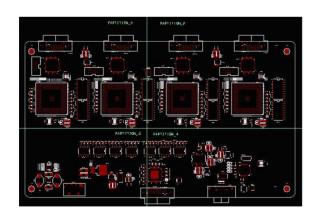

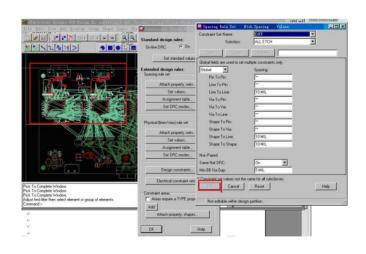

用 Allegro 打开 Partition 目录下的\*. dpf 文件,如下图所示,只有当前子设计区是高亮且可编辑,其它区域变灰。划分边界以GuidePort 为终点,进行布局布线。如果器件跨区域,会被Fixd不能移动。在子设计环境下,不能对设计电气、物理规则进行修改,当需要修改规则时,必须由 MASTER\_DESIGN 导入子设计后修改,如图所示。当子设完成后,进入 Place/Design Partition/Workflow Manager,修改 Progress 为 Complete,通知 MASTER DESIGN 导入子设计。

## 3. 合并设计

子设计完成后,打开 MASTER\_DESIGN 进入 Workflow Manager 选中需要导入的子模块,点击 Import 即可导入子设计。

## 4. 导入低版本子设计

并行设计周期中划分区域、合并设计了好几次,如果又想还原上一次划分区域的子设计,只要上次的子设计\*. dpf 原文件有备份,同时设计区域没有变化的条件下,可以钩选 Recovery Mode(恢复模式),点选上次的子设计导入即可。

## 5. 放弃导出的子设计

并行设计中,如果对其中的一个或多子设计需要放弃,那么只要选中相应的子设计点击 Retract (撤消选中的子设计)

#### 6. 册除子设计

删除子设计的方法同放弃子设计的操作方法一样,不同点是删除 子设计将会把划分区域删除。

## 四、总结

Allegro Partition设计过程中,子设计相互独立,只能通过 Report、Refresh了解其它设计进展,工程师必须有较好沟通。 划分区域边界不要有小缝隙,对设计重新划分区域时需要导入所 有子设计,导入导出要有周期性,设计中注意备份。

## Comtech 解决方案

- Cadence PCB 设计平台建设

- ECAD/CIS 库平台建设

- Allegro 软件二次开发

- PCB 项目设计及仿真外包服务

- Cadence 软件培训服务

# Comtech 优势

- 实力雄厚的资深技术团队, 多名 10 年以上经验的 FAE

- 丰富的 PCB 设计/EDA 平台建设等实践经验

- 出色的二次开发能力,为客户提供各种定制化开发需求

- 高效的技术服务平台,通过电话/邮件/Web/BBS,及时帮客 户解决各类软件使用/设计相关问题

- 实战指导、项目现场支持等特色服务

- 最新技术资料下载客户专享通道,包括软件使用技巧、设计经验、国外技术文献翻译等

- 为客户提供量身定制的全面的针对性培训服务

# 联系方式

#### 科通数字技术有限公司

- 总部:深圳市南山区高新南九道微软科通大厦 8-11 层

- 邮件: QipingWang@comtech.com.cn

- 地址:上海市徐汇区桂平路 426 号华鑫商务中心 2 号楼 7 层 03-04 室

- 华东地区

- 联系人: 陈敏敏 手机: 18017922811

- 邮件: PeterChen@comtech.com.cn

- 地址:上海市徐汇区桂平路 426 号华鑫商务中心 2 号楼 7 层 03-04 室

- 华南及西部地区

- 联系人: 谭波涛 手机: 15920086575

- 邮件: terrytan@comtech.com.cn

- 地址:深圳市南山区高新南九道微软科通大厦 8-11 层

- 华北地区

- 联系人: 党建成 手机: 18010161381

- 邮件: SudyDang@comtech.com.cn

- 地址:北京市海淀区中关村大街1号海龙大厦14层北区 1418-21