OrCAD FPGA System Planner

当工程师在PCB板上设计大规模引脚FPGA时,他们将遇到一些挑战:包括创建最初引脚分配、FPGA与原理图相结合、以及确保FPGA的合理布线。Cadence OrCAD FPGA System Planner正是为了应对如此的挑战,该模块为FPGA和PCB的协同设计提供了一个完整的、并具有可扩展性的解决方案,它能使以创建最优“器件-规则-准确”为目标的引脚分配过程自动进行。使用自动引脚分配综合技术来代替以前容易出错的手动操作过程,就可通过这个独特的布局解决方案减少在PCB板设计过程当中出现的反复迭代次数,同时缩短了创建最优引脚分配所需要的时间。

在PCB板上进行大规模引脚的FPGA设计

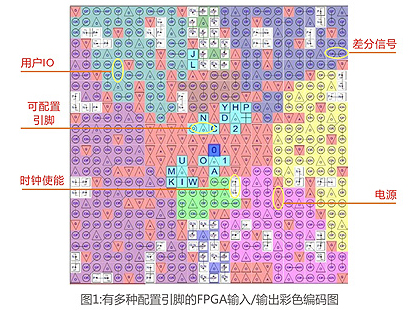

在PCB板上集成结构复杂的FPGA需要花费大量的时间,并且要延长设计周期,这些FPGA有很多不同种类的分配规则和需要用户配置的引脚,通常这些FPGA的引脚是用户通过手工操作一个挨着一个进行配置的,这些配置是在忽略PCB板上关键元件的摆放位置的情况下进行的,而这些关键元件恰恰是和FPGA相连接的。如果忽略以上操作给将来的PCB布线带来的影响,基于FPGA的设计工程将被迫面临两个困难的选择:非最优的引脚分配,这可能增加所设计的PCB板的叠层数;或者在设计周期的最后阶段要进行一些不必要的设计迭代。即使经过多次反复,这种较容易出错手动操作过程带来的后果仍然是不必要的PCB重复设计。

如果使用手动操作对FPGA的引脚进行分配,这将增加对FPGA进行引脚分配的时间,用户将不能在所提供的不同FPGA器件和其子系统当中使用的器件设计之间进行权衡,因为进行权衡意味着用户将同时处理两个不同工程,而他们两者之间并没有设计相互借鉴之处。

Cadence OrCAD FPGA System Planner为FPGA和PCB之间的协同设计提供了一种全面的、可扩展的解决方案,它能使用户创建一个正确的、最优的引脚分配。FPGA的引脚分配是根据用户的指定、基于接口的连接(设计目标)、FPGA的引脚分配规则(FPGA规则)和FPGA在PCB板上的实际位置(相对位置)来进行自动综合的。自动引脚分配综合避免了用户在手动操作过程当中容易出现的错误,同时缩短了在PCB板上创建FPGA初始引脚分配的时间(关系到被摆放的FPGA的引脚分配综合),这种独特的、关系到摆放位置的引脚分配方法消除了在手动操作过程当中容易出现的不必要的设计反复。

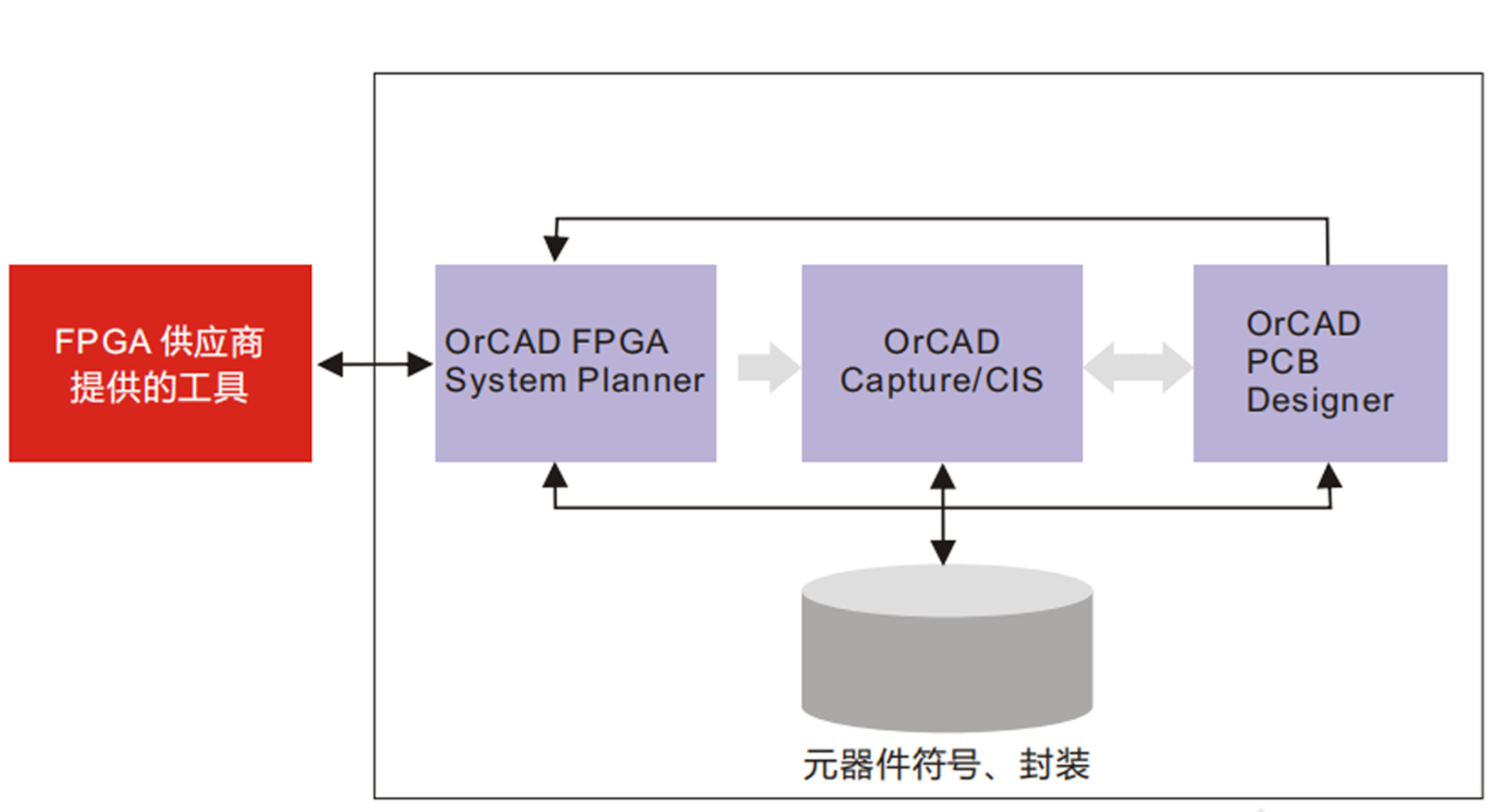

OrCAD FPGA System Planner集成在了OrCAD Capture和OrCAD PCB Editor当中,它可以读取Capture当中的原理图和元器件符号。另外,它可使用OrCAD PCB Editor当中现有的封装库。如果FPGA在布线过程中的摆放位置发生了变化,可在OrCAD PCB Editor当中直接调用FPGA System Planner进行的引脚优化。

功能特点

提供了从OrCAD到Allegro GXL、节约成本且具有可扩展性的FPGA-PCB协同设计解决方案。

缩短了进行最优初始引脚分配的时间,加快了PCB原理图的设计速度。

加快了FPGA和OrCAD设计环境的融合速度。

通过所放置的FPGA的引脚分配和优化来减少PCB板的层数。

OrCAD FPGA System Planner技术

一个FPGA系统是整个PCB电路板设计下面的一个组成部分,其中包括其他和该FPGA相连接的一个或多个FPGA,以及其他的非FPGA元件。

传统的引脚分配方法是典型的基于手动操作的引脚分配,或者常常要依靠一个电子表格来进行引脚分配。这些工具要求用户在不考虑其他元器件的摆放位置,以及接口和信号线的可布线性的情况下进行引脚分配。首先,没有在线规则检查能确保为FPGA引脚指定的信号线分配到的引脚种类是正确的。这样做带来的后果是,用户要在基于电子表格的工具和FPGA厂商提供的工具之间要进行很多的重复操作。

这样做影响到了在当前电路板层上不能完成对FPGA引脚进行布线的PCB布线设计者和接受这些PCB布线设计者纸面上或者口头上引脚分配建议的FPGA设计者,在他们两者之间常常增加很多不必要的重复操作。一旦FPGA设计者改变了最初的引脚分配,硬件设计者就得在所设计的原理图当中改变其引脚分配。这些不必要的重复操作将使设计周期延长几周或者几天的时间,同时给设计团队成员增加了很多麻烦。由于是手动操作过程,未发现的错误很可能导致电路板必须重新制作,这是十分昂贵的。

虽然FPGA设计者、硬件设计者和PCB布线设计者可同时对引脚分配作自动更改,但是这样做没有解决导致这些重复操作的根本问题。引脚分配并非受以下的的三个因素所制约:

FPGA资源可用性

FPGA供应商的引脚分配规则

以及FPGA在PCB板上的布线可行性——在设计进程的最后要进行很多的重复操作,从而延长了在PCB板上集成如今复杂的、大规模引脚FPGA所要花费的时间。

在设计进程的最后要进行很多的重复操作,从而延长了在PCB板上集成如今复杂的、大规模引脚FPGA所要花费的时间。